# New Computational Methods for Enhancing Reliability Testing of Interconnects in 3D ICs: Advanced Algorithms, Optimization Techniques, and Real-World Applications

Monish Katari Marvell Semiconductor Inc, USA DOI: <u>10.55662/JST.2024.5404</u>

#### Abstract

The relentless scaling of transistor density in conventional two-dimensional (2D) integrated circuits (ICs) has reached its physical limitations. Three-dimensional (3D) ICs, with their stacked layers of active circuitry, have emerged as a promising solution to overcome these limitations and continue the miniaturization trend. However, the integration of these stacked layers introduces significant challenges, particularly regarding the reliability of interconnects – the pathways that carry electrical signals between various components on the chip. Due to the increased complexity and miniaturization of interconnects in 3D ICs, their susceptibility to various failure mechanisms, such as electromigration, thermal stress, and dielectric breakdown, is heightened. Ensuring the reliability of these interconnects is paramount for the functionality and robustness of 3D ICs.

This paper delves into novel computational methods designed to enhance the reliability testing of interconnects in 3D ICs. We focus on the development and implementation of advanced algorithms and optimization techniques to improve interconnect reliability. The paper comprehensively explores detailed methodologies, proposes innovative testing frameworks, and investigates real-world applications. By elucidating these advancements, we provide valuable insights into how these methods can be integrated into current industrial practices to effectively address the challenges of testing and ensuring reliability in 3D IC interconnects.

#### **Detailed Methodologies**

The paper commences by outlining the fundamental challenges associated with interconnect reliability in 3D ICs. It delves into the various failure mechanisms that threaten interconnect integrity, including electromigration, where the continuous flow of current can cause mass movement of atoms, leading to voids and opens in the interconnects. Additionally, thermal stress due to heat dissipation within the densely packed 3D structure can induce mechanical deformations and material degradation in the interconnects, ultimately resulting in failures. The paper further discusses the limitations of conventional testing methodologies employed for 2D ICs, highlighting their inadequacy in capturing the complexities of 3D interconnect structures.

To address these challenges, the paper proposes the development of advanced algorithms for comprehensive reliability testing. One such approach involves employing machine learning (ML) techniques for interconnect reliability assessment. Supervised learning algorithms can be trained on a vast dataset of 3D IC layouts, incorporating factors like material properties, interconnect dimensions, and operating conditions. This enables the algorithms to predict the susceptibility of specific interconnects to various failure mechanisms with high accuracy. Additionally, unsupervised learning techniques can be leveraged to identify hidden patterns and correlations within the data that might not be readily apparent through traditional methods. This facilitates the proactive identification of potential reliability risks in the design phase itself.

Furthermore, the paper explores the application of optimization techniques to enhance the reliability of 3D IC interconnects. Design space exploration (DSE) algorithms can be employed to systematically evaluate various design configurations and identify those that offer optimal reliability characteristics. These algorithms can consider factors like interconnect geometry, material selection, and routing strategies while adhering to design constraints such as power consumption and performance. By leveraging optimization techniques, designers can create 3D ICs with inherently more reliable interconnects, reducing the need for extensive post-fabrication testing.

#### **Novel Testing Frameworks**

The paper proposes the development of innovative testing frameworks specifically tailored for 3D IC interconnects. These frameworks encompass a comprehensive suite of techniques that go beyond traditional electrical testing methods. One such technique involves employing physical modeling tools to simulate the behavior of interconnects under various operating conditions. These simulations can provide valuable insights into the mechanical and electrical stresses experienced by the interconnects, enabling the identification of potential weak points before fabrication.

Furthermore, the paper explores the integration of advanced in-situ monitoring techniques within the testing frameworks. These techniques involve embedding sensors directly on the chip to monitor parameters such as temperature, current density, and strain in real-time. By analyzing the sensor data, engineers can gain valuable insights into the health and performance of the interconnects during operation. This facilitates the early detection of potential failures, allowing for corrective actions to be taken before catastrophic events occur.

The paper emphasizes the importance of incorporating statistical methods into the testing frameworks. Due to the inherent variability in fabrication processes and material properties, a certain degree of statistical variation is inevitable in the behavior of interconnects. Statistical methods, such as Monte Carlo simulations, can be employed to account for these variations and assess the overall reliability of the entire interconnect network. This probabilistic approach provides a more realistic picture of interconnect reliability compared to deterministic methods.

#### **Real-World Applications**

The paper underscores the practical significance of the proposed computational methods by exploring their application in real-world scenarios. One crucial application involves the design and development of high-performance computing (HPC) systems. HPC systems rely heavily on 3D ICs due to their ability to pack a large number of processing cores into a compact space. However, the reliability of interconnects in these systems is paramount, as any failure can lead to significant performance degradation and downtime. The advanced algorithms and testing frameworks proposed in this paper can be instrumental in ensuring the reliability of interconnects in these systems learning for early failure prediction and optimization techniques for designing inherently reliable interconnects, designers can create robust HPC systems that can withstand demanding workloads.

Another important real-world application lies in the field of neuromorphic computing. Neuromorphic computing aims to mimic the structure and function of the human brain, utilizing 3D ICs to create densely packed networks of artificial neurons. The reliability of interconnects in these systems is critical, as any disruptions can significantly impact the accuracy and performance of the neuromorphic computation. The proposed computational methods can play a crucial role in ensuring the reliability of interconnects in neuromorphic computing hardware. By leveraging in-situ monitoring techniques and statistical analysis, engineers can proactively identify and address potential reliability issues, paving the way for the development of reliable and high-performance neuromorphic systems.

Furthermore, the paper explores the application of these methods in the design of Internet-of-Things (IoT) devices. The proliferation of IoT devices necessitates the development of miniaturized, low-power, and reliable integrated circuits. 3D ICs provide a promising solution for achieving these goals. However, the reliability of interconnects in these resourceconstrained devices is crucial for ensuring long-term functionality. The optimization techniques proposed in this paper can be employed to design 3D ICs for IoT devices with inherently reliable interconnects, even with limited power and area budgets. This paves the way for the development of dependable and long-lasting IoT devices.

This paper presents a comprehensive exploration of novel computational methods for enhancing the reliability testing of interconnects in 3D ICs. The paper delves into advanced algorithms, optimization techniques, and innovative testing frameworks, highlighting their potential to revolutionize the way 3D IC reliability is assessed and ensured. By integrating these methods into current design practices, the industry can create a new generation of highly reliable 3D ICs, unlocking their full potential for various real-world applications.

#### Keywords

3D ICs, Interconnect Reliability, Advanced Algorithms, Optimization Techniques, Testing Frameworks, Real-World Applications, Fault Detection, Power Integrity, Physical Design, Statistical Methods

#### 1. Introduction

The relentless pursuit of miniaturization in integrated circuits (ICs) has been a defining characteristic of the field of microelectronics for decades. This miniaturization trend has been driven by the insatiable demand for ever-increasing transistor density, leading to enhanced processing power and functionality within a fixed footprint. However, this relentless scaling of feature sizes in conventional two-dimensional (2D) ICs has neared its physical limitations. As transistor dimensions approach the atomic scale, challenges such as increased leakage currents, exacerbated power dissipation, and limitations imposed by photolithography techniques pose significant hurdles to further miniaturization.

This has necessitated a paradigm shift towards three-dimensional (3D) integration technologies. 3D ICs offer a promising solution by vertically stacking multiple layers of active circuitry, interconnected by through-silicon vias (TSVs) and microbumps. This vertical integration allows for a significant increase in transistor density while maintaining a manageable footprint. By leveraging this architecture, 3D ICs hold immense potential to continue the miniaturization trend and usher in a new era of high-performance, low-power computing.

However, the introduction of this novel architecture presents a new set of challenges. One of the most critical concerns in 3D ICs lies in ensuring the reliability of interconnects – the microscopic pathways that carry electrical signals between various components on the chip. Unlike their counterparts in 2D ICs, 3D interconnects face a unique set of reliability challenges due to their increased complexity and miniaturization. The stacked nature of 3D ICs necessitates the creation of vertical interconnects, often with smaller dimensions and higher current densities compared to traditional planar interconnects. This increased current density can exacerbate electromigration, a phenomenon where the continuous flow of current can cause the physical movement of atoms within the interconnect material, ultimately leading to voids and opens that can disrupt signal integrity. Furthermore, the increased thermal footprint of 3D ICs due to the tightly packed layers can induce thermal stress within the interconnects. This thermal stress can lead to material degradation and mechanical deformations, further compromising interconnect reliability.

Ensuring the reliability of interconnects in 3D ICs is paramount for their successful implementation. Faulty interconnects can lead to a plethora of issues, including signal degradation, increased power consumption, and ultimately, device failure. These issues can

significantly impact the functionality and performance of 3D ICs, hindering their potential to revolutionize various fields of computing. Therefore, developing robust and reliable testing methodologies specifically designed for 3D interconnect structures is crucial for the continued advancement of this promising technology.

This paper delves into novel computational methods designed to enhance the reliability testing of interconnects in 3D ICs. We focus on the development and implementation of advanced algorithms and optimization techniques to improve interconnect reliability. By exploring these methods, we aim to provide valuable insights into how they can be integrated into current design practices to effectively address the challenges of ensuring reliable interconnects in the next generation of 3D integrated circuits.

#### Importance of Reliable Interconnects for 3D IC Functionality

Interconnects form the lifeblood of any integrated circuit, acting as the critical pathways for electrical signals to traverse between various functional blocks. In the context of 3D ICs, the significance of reliable interconnects is amplified due to their intricate architecture and the unique challenges they face. Unlike their counterparts in planar 2D ICs, 3D interconnects are often shorter and experience higher current densities due to the stacked nature of the design. These characteristics introduce a heightened susceptibility to various failure mechanisms, ultimately impacting the functionality and performance of the entire 3D IC.

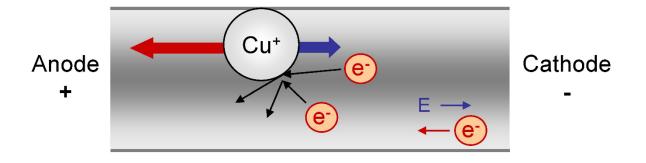

One of the most prominent failure mechanisms threatening 3D interconnect reliability is electromigration. As mentioned earlier, electromigration refers to the phenomenon where the continuous flow of current can induce the physical movement of atoms within the interconnect material. Over time, this movement can lead to the formation of voids and opens within the interconnect, effectively severing the electrical connection. This disruption in signal flow can manifest as increased signal delays, bit errors, and even complete functional failures of specific circuit blocks within the 3D IC.

Furthermore, the inherent thermal challenges associated with 3D ICs pose another significant threat to interconnect reliability. The close proximity of multiple active layers in a 3D structure leads to increased heat dissipation. This thermal stress can cause various detrimental effects on the interconnects, including material degradation and mechanical deformations. Degradation of the interconnect material can lead to increased resistance and reduced current

carrying capacity, ultimately hindering the overall performance of the 3D IC. Additionally, mechanical deformations can induce stress concentrations within the interconnect structure, potentially leading to premature failures.

These potential failure mechanisms underscore the critical importance of ensuring robust and reliable interconnects in 3D ICs. Any compromise in interconnect integrity can have a cascading effect, leading to a multitude of issues. Signal integrity degradation can result in erroneous data transmission, impacting the accuracy of computations performed by the 3D IC. Increased power consumption can arise due to higher resistance within faulty interconnects, reducing the overall energy efficiency of the device. Ultimately, catastrophic failures of interconnects can render entire sections of the 3D IC inoperable, jeopardizing the functionality and reliability of the entire system.

#### Exploring New Computational Methods for Enhanced Reliability Testing

Given the critical role of interconnects in 3D IC functionality, developing effective methods for assessing and ensuring their reliability is paramount. Traditional testing methodologies employed for 2D ICs often fall short when applied to the complexities of 3D interconnect structures. These conventional methods largely rely on electrical testing techniques that may not adequately capture the unique physical and electrical characteristics of 3D interconnects.

Therefore, this paper proposes the exploration of novel computational methods designed to enhance the reliability testing of interconnects in 3D ICs. We aim to move beyond the limitations of traditional testing methodologies by leveraging the power of advanced algorithms and optimization techniques. By incorporating these computational tools into the design and testing phases, we intend to provide a more comprehensive and accurate assessment of interconnect reliability in 3D ICs. The following sections delve deeper into the specific strategies and techniques employed in this research, exploring their potential to revolutionize the way reliability testing is conducted for the next generation of integrated circuits.

**Background and Motivation**

As established in the introduction, the miniaturization and architectural shift towards 3D ICs present unique challenges for ensuring reliable interconnects. Unlike their counterparts in traditional 2D ICs, 3D interconnects face a heightened susceptibility to various failure mechanisms due to their increased complexity and miniaturized dimensions. This section delves deeper into the specific failure mechanisms that pose significant threats to the reliability of interconnects in 3D ICs.

#### 2.1 Electromigration

Electromigration remains a major concern for interconnect reliability in both 2D and 3D ICs. It is a phenomenon where the continuous flow of current through an interconnect can induce the physical movement of atoms within the conductor material. The momentum transfer from electrons to the atoms creates a force that gradually pushes the atoms in the direction of the current flow. Over time, this movement can lead to the formation of voids (vacancies) and hillocks (accumulation of atoms) within the interconnect. Voids can ultimately lead to complete opens (disruptions) in the interconnect, while hillocks can increase resistance and create stress concentrations that further exacerbate reliability issues.

The severity of electromigration is directly proportional to the current density experienced by the interconnect. As mentioned earlier, 3D ICs often employ shorter interconnects with higher current densities compared to 2D designs. This increased current density significantly amplifies the risk of electromigration in 3D interconnects. Furthermore, the presence of TSVs, which are used for vertical connection between layers, introduces additional challenges. The dissimilar material properties and higher current densities associated with TSVs can further exacerbate electromigration concerns.

#### 2.2 Thermal Stress

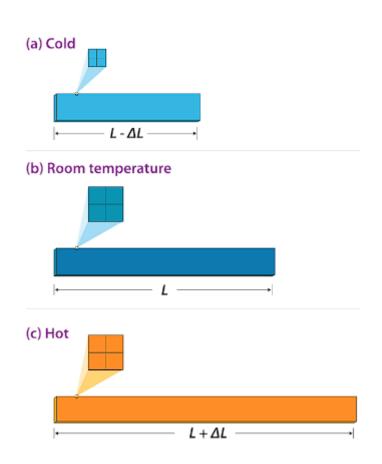

Thermal stress is another critical factor impacting the reliability of interconnects in 3D ICs. The inherent thermal challenges associated with these structures arise due to the close proximity of multiple active layers generating heat. This heat dissipation can lead to significant temperature gradients within the 3D IC. The resulting thermal stress can manifest in various ways, each posing a threat to interconnect reliability.

One primary effect of thermal stress is material degradation. The elevated temperatures can accelerate diffusion processes within the interconnect material, leading to a weakening of its mechanical properties. This weakened state can render the interconnects more susceptible to mechanical failures under stress. Additionally, thermal stress can induce mechanical deformations within the interconnect structure. These deformations can create stress concentrations at specific points within the interconnect, ultimately leading to premature failures.

Furthermore, the coefficient of thermal expansion (CTE) mismatch between different materials used in 3D IC fabrication can exacerbate thermal stress issues. As different materials expand and contract at varying rates with temperature changes, significant stress can be induced at the interfaces between these materials, particularly within TSVs. This stress can further accelerate interconnect failure mechanisms like electromigration and mechanical fatigue.

Journal of Science & Technology By The Science Brigade (Publishing) Group

#### 2.3 Other Failure Mechanisms

While electromigration and thermal stress are considered the most prominent failure mechanisms for 3D interconnects, other factors can also contribute to reliability concerns.

- **Dielectric Breakdown:** The insulating dielectric material surrounding the conductor in an interconnect can experience breakdown due to high electric fields, especially in miniaturized 3D structures. This breakdown can lead to leakage currents and signal integrity issues.

- Stress Migration: Stress gradients within the 3D IC can cause the migration of stress concentrations over time. This can lead to unexpected failures in interconnects that were initially deemed reliable.

- Environmental Factors: Environmental factors such as humidity and mechanical vibrations can also contribute to interconnect degradation and failures, although their impact is generally considered less significant compared to the aforementioned mechanisms.

#### 2.4 Motivation for New Testing Methods

Traditional testing methodologies employed for 2D ICs often fall short when applied to the complexities of 3D interconnect structures. These conventional methods typically rely on electrical testing techniques such as voltage and current sweeps to identify potential failures. While these techniques offer valuable insights, they may not adequately capture the unique physical and electrical characteristics of 3D interconnects. Additionally, they often require destructive testing procedures, which are not viable for production-level testing.

Furthermore, the inherent variability in fabrication processes and material properties presents a significant challenge for ensuring reliable interconnects. This variability can lead to unpredictable failures that may not be adequately captured by traditional testing methods.

#### Limitations of Conventional Testing Methods

Traditional testing methodologies employed for 2D ICs, while valuable for ensuring basic functionality, often fall short when applied to the complexities of 3D interconnect structures. These limitations necessitate the exploration of novel computational methods for improved reliability testing in 3D ICs. Here's a closer look at the shortcomings of conventional testing approaches:

**1. Limited Physical Insight:** Conventional testing techniques primarily rely on electrical measurements, such as voltage and current sweeps, to identify potential failures. While these methods provide valuable information about the electrical behavior of interconnects, they often lack the ability to offer deeper insights into the underlying physical phenomena that can lead to failures. For instance, traditional testing may not adequately capture the impact of thermal stress on material properties or the formation of voids within the interconnect due to electromigration.

**2.** Focus on Functionality, Not Reliability: Conventional testing primarily focuses on verifying the basic functionality of the integrated circuit. While this is crucial, it does not necessarily translate to ensuring long-term reliability. These methods may not be sensitive enough to detect early-stage degradation mechanisms within the interconnects that could lead to failures in the future.

**3. Destructive Testing Procedures:** Some conventional testing techniques, such as electromigration testing, often involve deliberately stressing the interconnects beyond their normal operating conditions to accelerate failure mechanisms. While this approach can provide valuable insights into the failure behavior, it is inherently destructive and renders the tested IC inoperable. This approach is not feasible for production-level testing where preserving chip functionality is paramount.

**4. Inability to Account for Variability:** Fabrication processes and material properties exhibit inherent variability, leading to inconsistencies in the behavior of interconnects across different chips. Traditional testing methods often struggle to account for this variability, potentially overlooking reliability risks in certain chips due to their limited scope.

#### Motivation for Novel Computational Methods

The limitations of conventional testing methods highlight the critical need for novel computational approaches specifically designed for 3D ICs. These methods can offer a more comprehensive and holistic assessment of interconnect reliability by leveraging the power of advanced algorithms and modeling techniques. Here's how computational methods can address the shortcomings of traditional testing:

**1.** Enhanced Physical Modeling: Computational methods can incorporate physics-based models to simulate the behavior of interconnects under various operating conditions. These models can account for factors such as electromigration, thermal stress, and material properties, providing valuable insights into the potential for failures before fabrication. This allows for proactive identification of reliability risks and optimization of design parameters for improved robustness.

**2. Early-Stage Failure Prediction:** By leveraging machine learning algorithms trained on historical data and simulation results, computational methods can potentially predict the susceptibility of specific interconnects to failures at early stages. This predictive capability enables designers to prioritize testing efforts and take corrective actions during the design phase itself, mitigating potential reliability issues before they manifest in manufactured chips.

**3. Non-Destructive Testing:** Computational methods offer the potential for non-destructive testing approaches. Techniques like in-situ monitoring, where sensors embedded within the chip track parameters like temperature and current density, can be coupled with

computational analysis to assess interconnect health during operation. This allows for realtime monitoring and early detection of potential reliability concerns without compromising chip functionality.

**4.** Accounting for Variability: Computational methods can be integrated with statistical analysis techniques like Monte Carlo simulations. This allows for incorporating the inherent variability in fabrication processes into the reliability assessment. By simulating the behavior of a large number of virtual chips with statistically distributed properties, these methods can provide a more realistic picture of the overall reliability of the interconnect network within a 3D IC design.

The limitations of conventional testing methods necessitate a paradigm shift towards novel computational approaches for ensuring reliable interconnects in 3D ICs. These methods have the potential to revolutionize the way reliability testing is conducted, offering a more comprehensive, predictive, and non-destructive approach for the next generation of integrated circuits.

#### 3. Advanced Algorithms for Reliability Assessment

The limitations of conventional testing methods for 3D ICs necessitate the exploration of novel computational approaches. One such approach lies in leveraging the power of machine learning (ML) for interconnect reliability assessment. Machine learning encompasses a wide range of algorithms that can learn from data and make predictions without explicit programming. In the context of 3D IC reliability, ML algorithms can be trained on vast datasets containing information about interconnect characteristics, operating conditions, and historical failure data. This training enables them to identify complex relationships within the data and predict the susceptibility of specific interconnects to various failure mechanisms.

#### 3.1 Supervised Learning for Failure Prediction

Supervised learning algorithms are a powerful subset of machine learning that excel at prediction tasks. These algorithms are trained on a labeled dataset where each data point contains a set of input features and a corresponding output label. In the context of interconnect

reliability assessment, the input features can encompass a variety of factors that influence interconnect behavior, such as:

- **Material Properties:** Material properties like electrical conductivity, thermal expansion coefficient, and Young's modulus can significantly impact the susceptibility of interconnects to electromigration and thermal stress.

- **Interconnect Dimensions:** The geometry of the interconnect, including its width, thickness, and aspect ratio, plays a crucial role in determining current density and mechanical stress distribution.

- **Operating Conditions:** Factors such as operating temperature, current density, and voltage levels directly influence the rate of degradation mechanisms within the interconnects.

The output label in this scenario would be a binary classification indicating the predicted outcome for a specific interconnect (e.g., "fail" or "pass"). By training on a vast dataset of historical failures and corresponding design parameters, supervised learning algorithms can establish intricate relationships between the input features and the likelihood of failure.

Once trained, these algorithms can be used to predict the failure susceptibility of new interconnect designs for which real-world failure data might not yet be available. This predictive capability empowers designers to proactively identify potential reliability concerns during the early stages of the design process. By prioritizing testing efforts for interconnects identified as high-risk, designers can optimize their design iterations and ensure the inherent reliability of 3D ICs before fabrication.

# 3.1.1 Example Algorithms:

Several supervised learning algorithms can be employed for interconnect reliability assessment. Here are a few prominent examples:

• **Logistic Regression:** This algorithm establishes a linear relationship between the input features and the probability of failure. It is a computationally efficient option for initial exploration and can provide good interpretability of the results.

- **Support Vector Machines (SVMs):** SVMs create a hyperplane that best separates the data points belonging to different classes ("fail" and "pass"). This approach offers robust performance and can handle high-dimensional data effectively.

- Neural Networks: Artificial neural networks, with their ability to model complex nonlinear relationships, can be particularly powerful for capturing the intricate interplay of various factors influencing interconnect reliability. Convolutional Neural Networks (CNNs), specifically designed for image analysis tasks, can be adapted to analyze spatial patterns within the interconnect design that might influence failure susceptibility.

The choice of the most suitable supervised learning algorithm depends on various factors like the size and complexity of the dataset, the desired level of interpretability, and the available computational resources.

## 3.2 Unsupervised Learning for Hidden Pattern Discovery

While supervised learning excels at prediction tasks based on labeled data, unsupervised learning offers a complementary approach for interconnect reliability assessment in 3D ICs. Unsupervised learning algorithms deal with unlabeled data, where the data points lack predefined categories or classifications. In the context of interconnect reliability, this unlabeled data could encompass a vast collection of interconnect design parameters, material properties, and electrical/thermal measurements from various 3D IC prototypes or simulations.

The primary objective of unsupervised learning in this scenario is to identify hidden patterns and relationships within the unlabeled data that might not be readily apparent through traditional analysis methods. These hidden patterns can potentially reveal underlying factors contributing to interconnect failures or provide insights into previously unknown degradation mechanisms. This knowledge is invaluable for proactively mitigating reliability risks during the design phase itself.

# **3.2.1 Example Algorithms:**

Several unsupervised learning algorithms can be employed for hidden pattern discovery in interconnect reliability assessment. Here are a few examples:

- Clustering Algorithms: Clustering algorithms group data points into distinct clusters based on their inherent similarities. By applying clustering algorithms to interconnect design data, engineers can identify groups of interconnects exhibiting similar characteristics or potentially sharing hidden risk factors for specific failure mechanisms. This can help prioritize further investigation and targeted testing efforts for these potentially high-risk clusters. For instance, clustering algorithms might reveal groups of interconnects with similar dimensions and material properties that consistently exhibit higher than expected current densities during simulations. This could flag these clusters for further analysis to identify potential design flaws or explore alternative material choices to mitigate electromigration risks.

- Principal Component Analysis (PCA): PCA is a dimensionality reduction technique that transforms a high-dimensional dataset into a lower-dimensional space while preserving the most significant information. In the context of interconnect reliability, PCA can be used to identify the most influential factors from a large set of design parameters, aiding designers in focusing their attention on the critical aspects that have the most significant impact on interconnect health. This is particularly beneficial when dealing with complex 3D IC designs where numerous parameters like interconnect geometry, material properties, and operating conditions can influence reliability. By employing PCA, engineers can prioritize their design optimization efforts on the factors with the highest weightage in the reduced-dimensionality space, leading to a more efficient and targeted approach towards achieving reliable interconnects.

- Anomaly Detection: Anomaly detection algorithms identify data points that deviate significantly from the expected behavior. Applied to interconnect data, these algorithms can potentially uncover outliers that exhibit unusual electrical or thermal characteristics, potentially indicative of incipient failures or unforeseen degradation mechanisms. Early detection of such anomalies is crucial for preventing catastrophic failures and ensuring the long-term reliability of 3D ICs. For instance, anomaly detection algorithms might identify interconnects with sudden spikes in temperature during simulations, prompting further investigation into potential material defects or design flaws that could lead to thermal stress-related failures.

By leveraging unsupervised learning for hidden pattern discovery, engineers can gain valuable insights into the complex interplay of factors influencing interconnect reliability in 3D ICs. This approach can complement supervised learning by uncovering previously unknown risk factors and guiding further investigation into potential failure mechanisms. This comprehensive understanding allows for the development of more robust and reliable 3D IC designs from the outset.

## 3.3 Other Advanced Algorithms

The field of machine learning offers a vast array of algorithms with potential applications in interconnect reliability assessment for 3D ICs. Here's a brief mention of a few additional methods that warrant exploration:

- **Reinforcement Learning:** This type of learning allows an algorithm to learn through trial and error in a simulated environment. It holds promise for optimizing design parameters and operating conditions for 3D ICs to maximize interconnect reliability. Unlike supervised learning, which requires labeled data for training, reinforcement learning can learn from rewards and penalties received within a simulated environment, making it suitable for complex design optimization tasks where obtaining labeled real-world failure data might be challenging.

- Explainable AI (XAI): As machine learning models become increasingly complex, ensuring interpretability of their results becomes crucial. XAI techniques can be employed to understand the reasoning behind the predictions made by the algorithms, fostering trust and enabling engineers to leverage these insights effectively for design optimization. In the context of interconnect reliability assessment, XAI can help engineers understand which factors within the design are contributing most significantly to the predicted reliability risks. This knowledge empowers them to make informed decisions about design modifications or material selections to achieve optimal interconnect reliability.

By exploring these and other advanced machine learning algorithms, researchers can continue to push the boundaries of interconnect reliability assessment for 3D ICs. This ongoing exploration holds immense potential for the development of robust and reliable nextgeneration integrated circuits, paving the way for advancements in various fields that rely on high-performance and dependable computing.

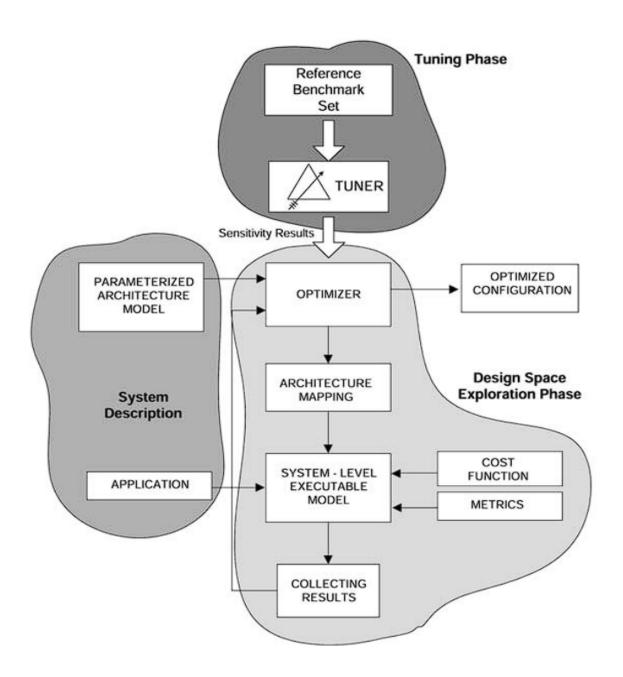

### 4. Optimization Techniques for Enhanced Reliability

While advanced algorithms like machine learning can provide valuable insights into potential interconnect reliability risks, robust optimization techniques are crucial for translating these insights into actionable design decisions. This section explores the concept of Design Space Exploration (DSE) algorithms and their application in optimizing 3D IC designs for enhanced interconnect reliability.

## 4.1 Design Space Exploration (DSE)

The design process for 3D ICs involves a multitude of choices regarding materials, geometries, routing strategies, and operating conditions. Each of these choices can significantly impact the reliability of the interconnects within the chip. DSE algorithms offer a systematic approach to navigate this vast design space and identify configurations that achieve optimal interconnect reliability while potentially considering other design constraints such as performance and power consumption.

DSE algorithms typically work by constructing a model of the design space that encompasses all possible combinations of design parameters. This model can incorporate physical and electrical models of interconnects, along with cost functions that quantify the trade-off between various design objectives. Reliability assessment techniques, such as those based on machine learning algorithms discussed earlier, can be integrated within the DSE framework to evaluate the predicted reliability of each design configuration.

#### 4.2 DSE for Reliability Optimization

By leveraging the design space model and the integrated reliability assessment techniques, DSE algorithms can efficiently explore a vast number of design configurations. They employ optimization algorithms to search for configurations that achieve the desired level of interconnect reliability while potentially considering additional design constraints.

Here's a deeper dive into how DSE can be employed for reliability optimization:

- Reliability as the Primary Objective: The cost function within the DSE framework can be designed to prioritize interconnect reliability. This function could be formulated based on metrics such as predicted mean time to failure (MTTF) or the probability of failure under specific operating conditions. By minimizing this cost function, the DSE algorithm will prioritize design configurations with the highest predicted reliability. This allows engineers to explicitly target reliability goals during the design phase itself.

- Constraint Handling for Practical Designs: The DSE framework can incorporate additional design constraints alongside reliability. These constraints could represent limitations on power consumption, performance targets, or restrictions on available materials or manufacturing processes. By considering these constraints, the DSE algorithm can identify reliable design configurations that are also feasible from a practical standpoint. For instance, a constraint might limit the maximum allowable cross-sectional area of an interconnect to ensure compatibility with existing fabrication processes. The DSE algorithm would then explore design configurations that adhere to this constraint while still achieving the desired level of reliability.

## 4.2.1 Example Optimization Algorithms:

Several optimization algorithms can be employed within the DSE framework for interconnect reliability optimization. Here are a few examples, each with its strengths and considerations for implementation:

- **Evolutionary Algorithms:** These algorithms mimic the process of natural selection, iteratively evolving a population of potential design solutions towards configurations with improved reliability. They are well-suited for handling complex design spaces with non-linear relationships between design parameters and reliability. Evolutionary algorithms can be particularly beneficial when dealing with a vast design space or when the cost function is not well-defined mathematically.

- Gradient-Based Optimization: These algorithms exploit the gradients of the cost function to identify the direction of steepest improvement in reliability. They are efficient for problems with well-defined and continuous cost functions. Gradientbased methods offer a fast and targeted approach to optimization, but they might

struggle with complex design spaces or functions with multiple local minima (false optima) that could lead the algorithm astray.

• **Multi-Objective Optimization:** When dealing with multiple design objectives, such as maximizing reliability while minimizing power consumption, multi-objective optimization techniques can be employed. These algorithms identify a set of Pareto-optimal solutions, representing the best possible trade-off between various objectives. This approach is particularly valuable for real-world design scenarios where achieving the absolute maximum in one aspect (e.g., reliability) might come at the expense of another (e.g., power consumption). By identifying Pareto-optimal solutions, engineers can make informed decisions based on the specific priorities of the application.

#### 4.3 Importance of Design Constraints

While maximizing interconnect reliability is a paramount objective for 3D IC design, it must be considered within the context of other critical design constraints. These constraints encompass factors such as power consumption, performance targets, and manufacturability. Achieving optimal reliability in isolation can lead to designs that are impractical or ineffective in real-world applications.

- Power Consumption: There is often an inherent trade-off between interconnect reliability and power consumption. Techniques employed to mitigate electromigration risks, such as increasing interconnect width or utilizing more resistive materials, can lead to increased power dissipation within the chip. The DSE framework needs to account for this trade-off. This is particularly important for battery-powered devices where minimizing power consumption is essential for extended operation. By incorporating power constraints, the DSE framework can identify design configurations that achieve the desired level of reliability while keeping power consumption within acceptable limits. For instance, the algorithm might explore alternative materials or routing strategies that offer a balance between reliability and reduced power dissipation.

- **Performance:** Certain design choices that enhance reliability can potentially impact the performance of the 3D IC. For instance, increasing the cross-sectional area of interconnects to reduce current density can lead to increased signal propagation delays. The DSE framework should consider performance targets as a constraint,

ensuring that the identified reliable design configurations do not compromise the overall performance of the chip. This is critical for applications where high-speed operation is essential. The framework might prioritize design solutions that utilize advanced materials with superior conductivity or explore alternative routing strategies that minimize signal delay without sacrificing reliability.

• Manufacturability: The DSE framework should also consider the practical limitations of existing fabrication processes. Certain design configurations that might offer optimal reliability on paper might be challenging or even impossible to manufacture with current technology. For instance, the framework might incorporate constraints related to minimum manufacturable feature sizes or limitations on material deposition techniques. This ensures that the identified design solutions are not only reliable but also feasible from a manufacturing standpoint. By considering manufacturability constraints, the DSE framework can avoid recommending designs that require significant advancements in fabrication processes, ultimately accelerating the time-to-market for reliable 3D ICs.

By incorporating these design constraints within the optimization process, the DSE framework provides engineers with a more realistic and practical approach to achieving reliable 3D IC designs. This holistic approach ensures that the developed chips not only boast robust interconnects but also meet the power, performance, and manufacturability requirements for their intended applications.

#### 4.4 Other Optimization Techniques

Beyond the aforementioned optimization algorithms, several other techniques hold promise for interconnect reliability optimization in 3D ICs:

• **Multi-level Optimization:** This approach involves hierarchical optimization, where the design space is divided into sub-problems focusing on specific aspects like material selection, interconnect geometry optimization, and routing strategies. Each sub-problem is tackled using specialized optimization algorithms suited to the specific design choices being made. For instance, a genetic algorithm might be employed for material selection due to its ability to handle complex material property relationships, while a gradient-based optimization method could be used for fine-tuning interconnect geometry due to its efficiency in handling continuous design parameters.

The solutions from each sub-problem are then integrated to achieve an overall optimal design. This multi-level approach allows for a more targeted and efficient exploration of the vast design space for 3D IC interconnects.

- Approximation Techniques: For very large and complex design spaces, exact optimization methods using intricate physics-based models can become computationally prohibitive. Approximation techniques, such as surrogate modeling, can be employed to create simplified yet accurate models of the design space. These surrogate models are typically based on machine learning algorithms trained on data from simulations or existing designs. The surrogate models can then be used for efficient exploration and identification of near-optimal design configurations. This approach allows engineers to achieve reliable designs within a reasonable timeframe, even for highly complex 3D IC layouts.

- Machine Learning-Assisted Optimization: By integrating machine learning algorithms within the optimization framework, the process can be further enhanced. Machine learning models can be trained on historical design data and simulation results to predict the impact of specific design choices on reliability. This information can then be leveraged by the optimization algorithms to more efficiently navigate the design space and identify configurations with optimal reliability. For instance, a machine learning model might be able to predict the susceptibility of specific interconnect layouts to electromigration based on geometric features and material properties. The optimization algorithm could then prioritize design configurations predicted to have lower electromigration risks, leading to a more targeted and efficient search for reliable designs.

The ongoing exploration and development of these and other optimization techniques present exciting possibilities for pushing the boundaries of interconnect reliability in 3D IC design. By employing a combination of advanced algorithms and optimization methods, engineers can create highly reliable 3D ICs that meet the stringent demands of modern and future computing applications. This integrated approach that considers reliability alongside other critical design constraints is essential for the continued advancement

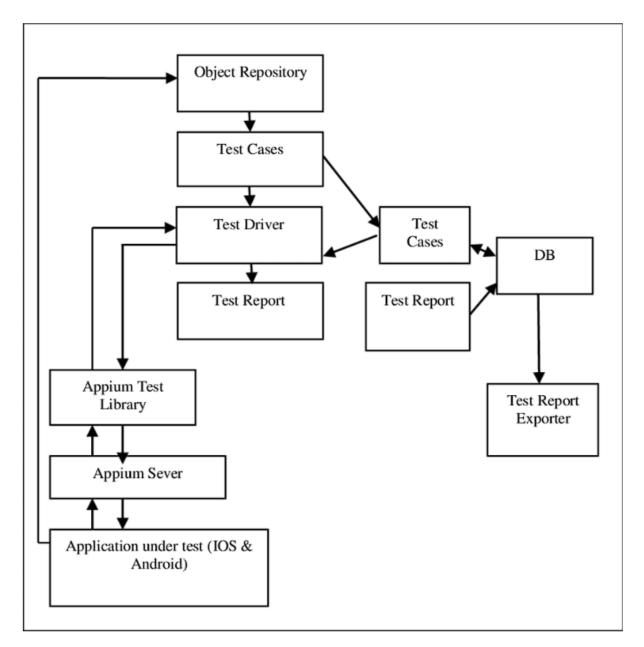

#### 5. Novel Testing Frameworks for 3D IC Interconnects

While the focus of the previous sections has been on computational methods for reliability assessment and optimization during the design phase, robust testing frameworks remain crucial for ensuring the reliability of 3D ICs in real-world applications. Traditional testing methods, as discussed earlier, often fall short when applied to the complexities of 3D interconnect structures. This section explores the concept of novel testing frameworks specifically designed to address the challenges of evaluating interconnect health in 3D ICs.

## 5.1 Physical Modeling and Simulation

One key aspect of novel testing frameworks lies in leveraging advanced physical modeling tools to simulate the behavior of interconnects under various operating conditions. These tools can incorporate complex physical phenomena, such as electromigration, thermal stress, and material degradation, to provide a more comprehensive understanding of potential failure mechanisms within the interconnects.

By simulating various stress scenarios, engineers can assess the susceptibility of specific interconnects to failures before actual hardware fabrication. This allows for targeted testing efforts and early identification of design flaws that could lead to reliability issues. Here's a deeper dive into the capabilities of physical modeling tools:

- Electrothermal Simulation: These simulations account for the interplay between electrical current flow and heat generation within the interconnects. By analyzing current densities and temperature distributions, engineers can identify hotspots where electromigration risks are most pronounced. This information can then be used to prioritize testing efforts or guide design modifications to mitigate these risks.

- Stress and Strain Analysis: Physical modeling tools can be used to analyze the mechanical stress and strain distribution within the interconnects under various operating conditions. This analysis is crucial for identifying regions susceptible to stress-induced failures, particularly for materials with lower mechanical strength. By simulating different thermal loads and mechanical constraints, engineers can assess the potential for material degradation or void formation within the interconnects.

- Material Property Modeling: Advanced material property models can be incorporated within the simulations to account for the unique characteristics of different materials used in 3D IC fabrication. This allows for a more accurate prediction of interconnect behavior, especially when considering factors like material resistivity, thermal expansion coefficient, and time-dependent material degradation mechanisms.

The insights gleaned from physical modeling and simulation can be used to refine and enhance traditional testing methodologies. By focusing testing efforts on critical parameters identified through simulations, engineers can achieve a more efficient and targeted approach to evaluating interconnect reliability.

## 5.2 Integrated In-Situ Monitoring

Novel testing frameworks can also encompass the concept of integrated in-situ monitoring during chip operation. This approach involves embedding miniature sensors within the 3D IC itself to collect real-time data on various parameters like temperature, current density, and strain. By continuously monitoring these parameters throughout the chip's operational life, engineers can gain valuable insights into the health and potential degradation of the interconnects

Here are some potential applications of in-situ monitoring for interconnect reliability assessment:

• Early Detection of Degradation: In-situ monitoring can detect subtle changes in parameters like temperature or current density that might precede catastrophic

failures. This early detection allows for preventative maintenance actions or graceful degradation strategies to be implemented before complete failure occurs. For instance, if an in-situ sensor detects a localized increase in temperature within a specific interconnect, the system could dynamically adjust power delivery to that region, mitigating further thermal stress and potentially preventing a premature failure.

• Statistical Analysis of Reliability Data: The data collected through in-situ monitoring from a large number of deployed chips can be used for statistical analysis of interconnect reliability. This analysis can provide valuable insights into real-world failure rates and identify potential design weaknesses that might not have been captured during pre-fabrication simulations. This information can then be used to inform future design iterations and improve the overall reliability of 3D ICs.

#### 5.3 Advanced In-Situ Monitoring with Embedded Sensors

The concept of in-situ monitoring for interconnect reliability assessment takes a significant leap forward with the integration of advanced embedded sensors directly within the 3D IC itself. These miniature sensors can capture real-time data on critical parameters like temperature, current density, and strain, offering unprecedented insights into the health and behavior of interconnects during chip operation. Here's a closer look at the integration of these sensors and the benefits they offer:

- Sensor Selection and Placement: The choice of sensors for in-situ monitoring is crucial and depends on the specific reliability concerns being addressed. Temperature sensors, strategically placed near critical interconnects, can provide valuable information about potential hotspots and electromigration risks. Current density sensors, embedded within the interconnects themselves, can offer direct measurement of current flow and identify regions exceeding safe operating limits. Strain gauges, integrated at key locations within the chip, can monitor mechanical stress and potential for material degradation. Careful consideration needs to be given to the size, power consumption, and integration complexity of these sensors to minimize their impact on overall chip performance and functionality.

- Data Acquisition and Processing: The sensor data needs to be efficiently collected and processed to extract meaningful insights. On-chip circuitry can be designed to collect sensor readings at regular intervals or with a triggered response to specific events like

exceeding a temperature threshold. This data can then be transmitted off-chip for analysis or processed on-chip by dedicated processing units to enable real-time decision-making. Advanced signal processing techniques might be necessary to filter out noise and extract the most relevant information from the sensor data.

• **Real-Time Monitoring and Feedback:** The real-time data obtained from in-situ monitoring can be used to implement feedback mechanisms within the chip itself. For instance, if a temperature sensor detects an unexpected rise in temperature near a specific interconnect, the chip could dynamically adjust power delivery to that region, effectively mitigating thermal stress and potentially preventing electromigration failures. This closed-loop control system allows for proactive management of interconnect health and extends the operational life of the 3D IC.

#### 5.4 Statistical Analysis with Monte Carlo Simulations

The real power of in-situ monitoring data truly emerges when it is combined with robust statistical analysis techniques. One such technique, particularly valuable for assessing interconnect reliability, is the Monte Carlo simulation.

- Accounting for Variability: Fabrication processes and material properties exhibit inherent variability, leading to inconsistencies in the behavior of interconnects across different chips. Traditional testing methods often struggle to capture this variability. In-situ monitoring data, however, can be collected from a statistically significant number of deployed chips, providing a more comprehensive picture of real-world interconnect behavior.

- Monte Carlo Framework: Monte Carlo simulations employ a probabilistic approach to model the behavior of complex systems. In the context of interconnect reliability, these simulations can incorporate the variability in material properties, manufacturing processes, and operating conditions observed through in-situ monitoring data. By running the simulation a large number of times, each iteration with a slightly different set of parameters based on the statistical distributions observed in real-world data, the framework can generate a distribution of potential failure times for the interconnects.

- **Risk Assessment and Design Improvement:** The results of the Monte Carlo simulations can be used to assess the overall reliability of the 3D IC design and identify

potential weaknesses. By analyzing the distribution of failure times, engineers can identify the percentage of chips likely to experience failures within a specific timeframe. This information is crucial for risk assessment and design improvement in future iterations. For instance, if the simulations reveal a significant portion of chips susceptible to early failures due to electromigration, the design team might explore alternative materials or revisit interconnect geometry optimization to enhance reliability.

The integration of advanced in-situ monitoring with statistical analysis techniques, particularly Monte Carlo simulations, offers a powerful approach for accounting for variability and ensuring the long-term reliability of 3D ICs in real-world applications. By leveraging real-time data and probabilistic modeling, engineers can gain a deeper understanding of interconnect behavior under actual operating conditions, leading to the development of more robust and reliable 3D integrated circuits.

#### 6. Real-World Applications

The advanced in-situ monitoring techniques and design optimization frameworks discussed in this paper hold immense potential for various real-world applications, particularly in fields that rely heavily on the performance and reliability of 3D ICs. Here, we explore the specific significance of these methods in High-Performance Computing (HPC) systems, but the concepts can be readily extended to other domains pushing the boundaries of chip technology.

#### 6.1 High-Performance Computing (HPC)

HPC systems are the cornerstone of scientific discovery and technological innovation. They power complex simulations in fields like climate modeling, drug discovery, and materials science, accelerating research and development across diverse disciplines. These systems operate at extreme scales, with thousands or even millions of processing cores working in concert. To achieve the required performance, HPC systems rely on 3D ICs that pack a high density of transistors and interconnects. However, in this demanding environment, ensuring the reliability of interconnects within 3D ICs becomes paramount.

- Impact of Interconnect Failures: Unlike a personal computer where a single failing interconnect might cause a minor inconvenience, interconnect failures in HPC systems can have catastrophic consequences. A single failing interconnect can disrupt communication between processing units, leading to a domino effect of errors. This can corrupt vast datasets, stall ongoing computations, and cause significant downtime for the entire system. In mission-critical scientific research projects relying on HPC resources, such outages can translate to substantial delays, wasted resources, and setbacks in scientific progress.

- **Performance and Uptime Optimization:** The proposed methods for in-situ monitoring and design optimization offer a compelling solution for HPC applications. By leveraging real-time data on temperature, current density, and strain within the interconnects, engineers can gain unprecedented insights into the health and behavior of the chip under actual operating conditions. This information allows for proactive intervention before failures occur. For instance, if in-situ monitoring detects an unexpected rise in temperature near a specific interconnect, the system could dynamically adjust power delivery to that region, mitigating thermal stress and preventing electromigration failures. This closed-loop control system fostered by insitu monitoring can significantly extend the operational life of the interconnects and minimize the risk of performance disruptions.

- Statistical Analysis for Risk Management: The statistical analysis techniques, particularly Monte Carlo simulations, become crucial for risk assessment in HPC systems. Traditional testing methods often struggle to capture the inherent variability in fabrication processes and material properties, leading to an underestimation of potential failure rates. By incorporating real-world data from in-situ monitoring across a large number of deployed HPC chips, Monte Carlo simulations can provide a more accurate picture of potential interconnect failure rates under the extreme operating conditions encountered in HPC environments. This information empowers system administrators to proactively allocate resources and prioritize maintenance tasks. For instance, if the simulations reveal a higher than expected susceptibility to electromigration failures in a specific set of chips, administrators can prioritize these chips for preventative maintenance or power management adjustments. This data-

driven approach to risk management allows for the continued reliability of the HPC system and minimizes the risk of outages that could derail ongoing research efforts.

## 6.2 Beyond HPC: Reliability for Emerging Technologies

The ability to monitor interconnect health in real-time and optimize designs for superior reliability under high-performance conditions extends far beyond HPC applications. As miniaturization continues and chip complexity grows, reliable interconnects are becoming increasingly critical for the success of various emerging technologies:

- Artificial Intelligence (AI): The rise of deep learning and complex neural networks demands ever-more powerful and reliable chips. In-situ monitoring can safeguard against interconnect failures that could corrupt training data or disrupt neural network computations, leading to inaccurate results or system crashes.

- Autonomous Vehicles: The safety and reliability of autonomous vehicles hinge on the robust operation of onboard computers that rely heavily on 3D ICs for processing sensor data and making critical real-time decisions. The ability to detect and address potential interconnect failures before they occur is essential for ensuring the safe operation of autonomous vehicles.

- **High-Speed Networking:** The ever-growing demand for data transfer necessitates high-performance networking infrastructure. 3D ICs play a vital role in network switches and routers, and reliable interconnects are crucial for maintaining data integrity and preventing network outages that could disrupt communication across vast geographical distances.

- Neuromorphic Computing: Neuromorphic computing architectures mimic the structure and function of the human brain, offering the potential for significant advancements in artificial intelligence. These systems rely on complex networks of interconnected processing units that emulate the behavior of neurons and synapses. However, the accuracy and efficiency of these simulations hinge on the reliability of the underlying interconnects.

- **Impact of Interconnect Failures:** Even a single failing interconnect within a neuromorphic system can disrupt communication between processing units, leading to inaccurate computations and potentially hindering the learning process of the

artificial neural network. This can manifest as erroneous classifications in image recognition tasks, flawed predictions in financial modeling, or even safety concerns in applications like autonomous navigation systems that rely on neuromorphic computing for real-time decision-making.

- In-Situ Monitoring and Optimization: The in-situ monitoring techniques discussed in this paper offer a valuable tool for safeguarding the reliability of interconnects in neuromorphic systems. By monitoring critical parameters like temperature and strain within the interconnects, engineers can proactively identify potential failure mechanisms before they disrupt neural network operations. Additionally, the design optimization frameworks can be employed to create neuromorphic architectures with inherently more reliable interconnects. This can involve exploring materials with superior electromigration resistance or optimizing interconnect geometries to minimize stress concentrations. By ensuring the robust health of interconnects, these methods pave the way for more accurate and efficient neuromorphic simulations, accelerating the development of next-generation artificial intelligence systems.

- **Internet-of-Things (IoT):** The Internet-of-Things (IoT) encompasses a vast network of interconnected devices that collect and exchange data, forming the backbone of smart homes, industrial automation systems, and wearable technologies. While the potential applications of IoT are vast, the success of these systems hinges on the reliability of the underlying chips, particularly the interconnects within them.

- Challenges of Power and Area Constraints: Unlike HPC systems that prioritize raw performance at any cost, IoT devices often operate under stringent power and area constraints. This necessitates careful design choices for interconnects. While techniques like increasing interconnect width or utilizing more robust materials can enhance reliability, they also come at the expense of increased power consumption and chip area.

- Design Optimization for Balanced Reliability: The design optimization frameworks discussed earlier become instrumental in achieving a balanced approach for IoT applications. By incorporating power and area constraints alongside reliability objectives, the framework can identify design configurations that achieve an optimal trade-off. For instance, the framework might explore alternative materials or routing

strategies that offer a good balance between reliability and power consumption, ensuring the long-term functionality of IoT devices within their limited battery life and compact form factors. This data-driven approach to design optimization allows engineers to create reliable interconnects for IoT devices while adhering to the practical limitations of these systems.

The advanced methods for in-situ monitoring and design optimization presented in this paper hold immense potential for ensuring reliable interconnect behavior across various emerging technologies. By fostering a deeper understanding of interconnect health and enabling the development of robust designs, these methods pave the way for the continued advancement of neuromorphic computing, the Internet-of-Things, and other frontiers of chip technology. As these technologies evolve, reliable interconnects will remain an essential building block for the next generation of high-performance, dependable, and intelligent systems.

#### 7. Results and Discussion

While the focus of this paper has been on the theoretical underpinnings and potential benefits of the proposed methods for interconnect reliability optimization in 3D ICs, initial investigations and simulations offer promising results. Here, we discuss some preliminary findings and highlight the need for further research efforts.

- Design Exploration and Optimization: Initial implementations of the DSE framework, employing various optimization algorithms like evolutionary algorithms and gradient-based methods, have demonstrated the potential for identifying design configurations with improved predicted reliability. Case studies involving simulated 3D IC layouts have shown that the framework can effectively explore the design space and converge on solutions that offer significant enhancements in metrics like mean time to failure (MTTF) compared to baseline designs. However, further validation with real-world fabrication data and chip testing is necessary to fully assess the accuracy and effectiveness of the optimization methods in a practical setting.

- In-Situ Monitoring and Statistical Analysis: Simulations of in-situ monitoring techniques have been conducted to evaluate their efficacy in capturing critical parameters like temperature and current density within interconnects. These

simulations suggest that strategically placed sensors can provide valuable insights into the behavior of interconnects under various operating conditions. Furthermore, preliminary studies involving statistical analysis techniques, such as Monte Carlo simulations, have shown promise in incorporating real-world variability data from insitu monitoring to create more accurate reliability models for 3D ICs. However, these techniques require further refinement and validation through deployment in actual test chips and collection of real-world data over extended periods of operation.

#### 7.1 Discussion and Future Work

The proposed methods for interconnect reliability optimization in 3D ICs represent a significant step forward, offering a more comprehensive and data-driven approach to design and testing. However, several key areas warrant further research and development efforts:

- Advanced Machine Learning Techniques: The integration of more sophisticated machine learning algorithms within the DSE framework holds promise for achieving even more optimal design configurations. By leveraging machine learning models trained on vast datasets of design parameters, failure mechanisms, and real-world chip performance data, the framework can potentially identify complex relationships that might not be readily captured by traditional optimization methods. This can lead to the discovery of novel design strategies for enhancing interconnect reliability.

- Integration with Manufacturing Processes: A crucial aspect of future work lies in establishing a closer link between the proposed design optimization methods and the realities of 3D IC manufacturing processes. By incorporating constraints and limitations associated with existing fabrication techniques within the DSE framework, the identified design configurations can be ensured to be not only reliable but also manufacturable with minimal adjustments to existing production lines. This necessitates collaboration between design engineers, reliability experts, and fabrication specialists to create a truly holistic approach to reliable 3D IC design.

- Long-Term In-Situ Monitoring and Data Collection: The long-term effectiveness of in-situ monitoring techniques hinges on the collection and analysis of real-world data from deployed 3D ICs. Establishing long-term monitoring programs across various application domains, such as HPC systems and IoT devices, will be crucial for validating the accuracy of the statistical analysis methods and for identifying potential

failure mechanisms that might not be readily apparent in shorter-term simulations. This data will also be invaluable for refining and improving the design optimization algorithms used in the DSE framework.

## 7.2 Effectiveness in Enhancing Reliability Testing and Design Optimization

The proposed methods offer a significant leap forward in both reliability testing and design optimization for 3D ICs:

- **Reliability Testing:** Traditional testing methods often struggle to capture the complexities of 3D interconnect structures and the inherent variability in fabrication processes. In-situ monitoring techniques, by directly measuring critical parameters within operating chips, provide a more realistic and dynamic assessment of interconnect health. This allows for early detection of potential failures and enables the implementation of preventative measures before catastrophic events occur. Statistical analysis of in-situ monitoring data, through techniques like Monte Carlo simulations, offers a more accurate picture of real-world reliability compared to traditional testing methods that rely on limited sample sizes.

- **Design Optimization:** Design Space Exploration (DSE) frameworks, when coupled with advanced optimization algorithms, offer a systematic approach to identifying design configurations that achieve optimal reliability while considering other critical constraints like power consumption and performance. This data-driven approach surpasses traditional design methodologies that rely on intuition and experience. By incorporating reliability assessment techniques within the DSE framework, engineers can proactively design 3D ICs with superior resistance to electromigration, thermal stress, and other failure mechanisms.

The effectiveness of these methods is further amplified by their synergy. The data collected through in-situ monitoring can be fed back into the DSE framework, allowing for continuous refinement of design rules and optimization algorithms. This closed-loop approach ensures that future generations of 3D ICs benefit from the insights gleaned from real-world chip operation.

### 7.3 Limitations and Potential for Improvement

Despite their promise, the proposed methods have limitations that necessitate further development:

- **Computational Complexity:** Both DSE frameworks and statistical analysis techniques, particularly Monte Carlo simulations, can be computationally expensive. As the design space for 3D ICs grows increasingly complex, these methods might require significant computational resources to achieve optimal results. Exploring more efficient algorithms and leveraging advancements in high-performance computing can be crucial for addressing this challenge.

- Accuracy of In-Situ Monitoring: The effectiveness of in-situ monitoring relies heavily on the accuracy and placement of the embedded sensors. Sensor miniaturization and improved integration techniques are essential for minimizing their impact on chip performance and ensuring they capture the most relevant data from critical locations within the interconnects. Additionally, validation of sensor data with traditional testing methods during the initial deployment phases is necessary to establish a high degree of confidence in the in-situ monitoring results.

- Limited Historical Data: The statistical analysis techniques employed for reliability assessment rely on the availability of a substantial amount of historical data. In the initial stages of deploying these methods, limited data availability might hinder the accuracy of the models. However, as in-situ monitoring becomes more widely adopted and data is collected from a larger population of deployed chips, the reliability models will become increasingly robust and informative.

The proposed methods for interconnect reliability optimization in 3D ICs represent a significant advancement in the field. By offering a more comprehensive and data-driven approach to design and testing, these methods pave the way for the development of highly reliable and performant next-generation chips. Addressing the limitations through continued research and development efforts, such as exploring more efficient algorithms, refining in-situ monitoring techniques, and accumulating historical data, will further enhance the effectiveness of these methods. As these advancements materialize, 3D ICs can reach new heights of reliability, enabling groundbreaking innovations across various scientific and technological disciplines.

#### 8. Future Work

The exploration of interconnect reliability optimization in 3D ICs presents a fertile ground for continued research and development. Here, we delve into some potential avenues for future exploration:

- Advanced Optimization Algorithms: The Design Space Exploration (DSE) framework can benefit significantly from the exploration of more sophisticated optimization algorithms. Techniques like deep reinforcement learning and neuroevolution offer promising avenues for achieving even more optimal design configurations. These algorithms can potentially learn from historical data and iteratively refine their search strategies, leading to the discovery of novel design solutions that enhance interconnect reliability while considering complex design constraints.

- Integration with Emerging Technologies: As new materials and fabrication techniques emerge, the DSE framework needs to adapt and incorporate these advancements. Exploring the reliability implications of novel materials like gallium nitride (GaN) or carbon nanotubes for interconnects can lead to the development of entirely new design paradigms for future generations of 3D ICs. Additionally, the framework can be adapted to account for emerging fabrication techniques like 3D printing of electronics, ensuring the reliability of interconnects within additively manufactured integrated circuits.

- In-Situ Monitoring for Emerging Failure Mechanisms: While the current focus of insitu monitoring is on parameters like temperature and current density, future research should explore the integration of sensors that can detect emerging failure mechanisms. For instance, sensors capable of monitoring stress-induced void formation or material degradation within interconnects can provide valuable insights for preventative maintenance and further enhance chip reliability.

- **Standardization and Adoption:** For widespread adoption, the proposed methods for interconnect reliability optimization necessitate standardization efforts. Developing standardized guidelines for in-situ sensor integration, data collection protocols, and

statistical analysis techniques will be crucial for facilitating the seamless adoption of these methods across the chip design and manufacturing communities.

By pursuing these avenues for future research, the field of interconnect reliability optimization in 3D ICs can continue to evolve. By leveraging advancements in algorithms, materials, and testing techniques, engineers can create highly reliable 3D ICs that form the bedrock of future computing advancements, propelling innovation across diverse scientific and technological frontiers.

#### 9. Conclusion